Man läser överallt att elektroniken bara blir mindre och mindre för att den följer Moores lag. Det har varit sant hittills, men nu har tillverkarna kört in i en fysikalisk gräns. Det har börjat bli svårt och framför allt dyrt att göra transistorer mindre än 5 nanometer utan att behöva ta till extrema metoder och maskiner.

Då byter man synsätt. Återigen gör svensk halvledarforskning ett genombrott. In kommer KTH i Kista och långa arbetspass i Myfabs renrum Electrumlab. Det skulle visa sig att ansträngningen var värd allt arbete.

Jag har sagt det förut och säger det igen: Det finns inget en KTH-doktorand inte kan åstadkomma, bara hon lägger manken till!

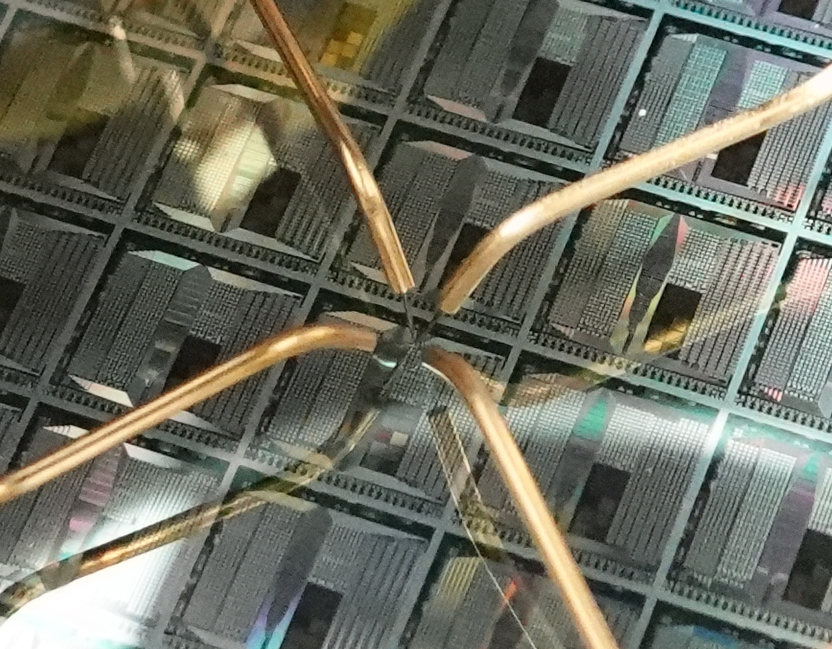

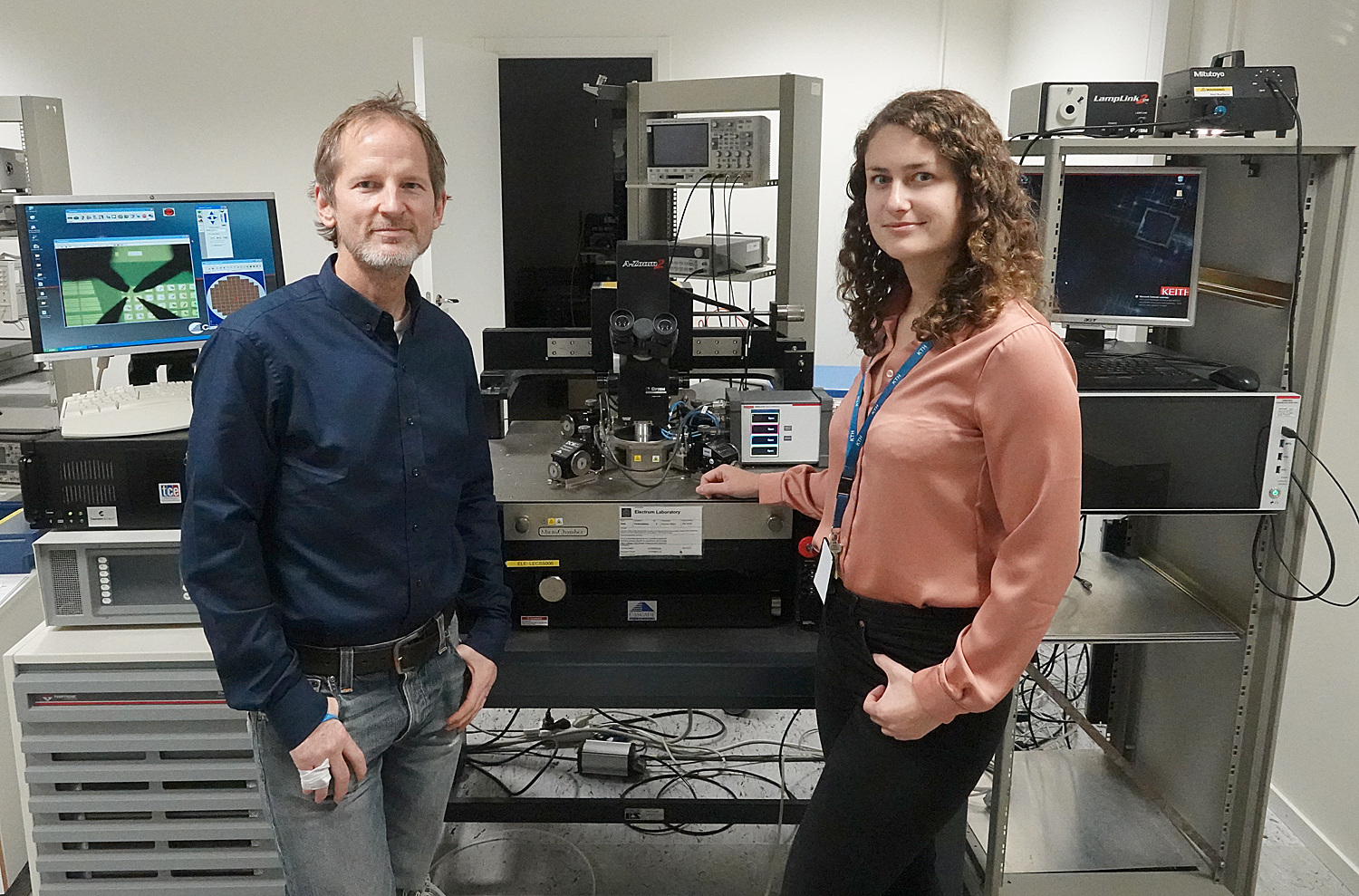

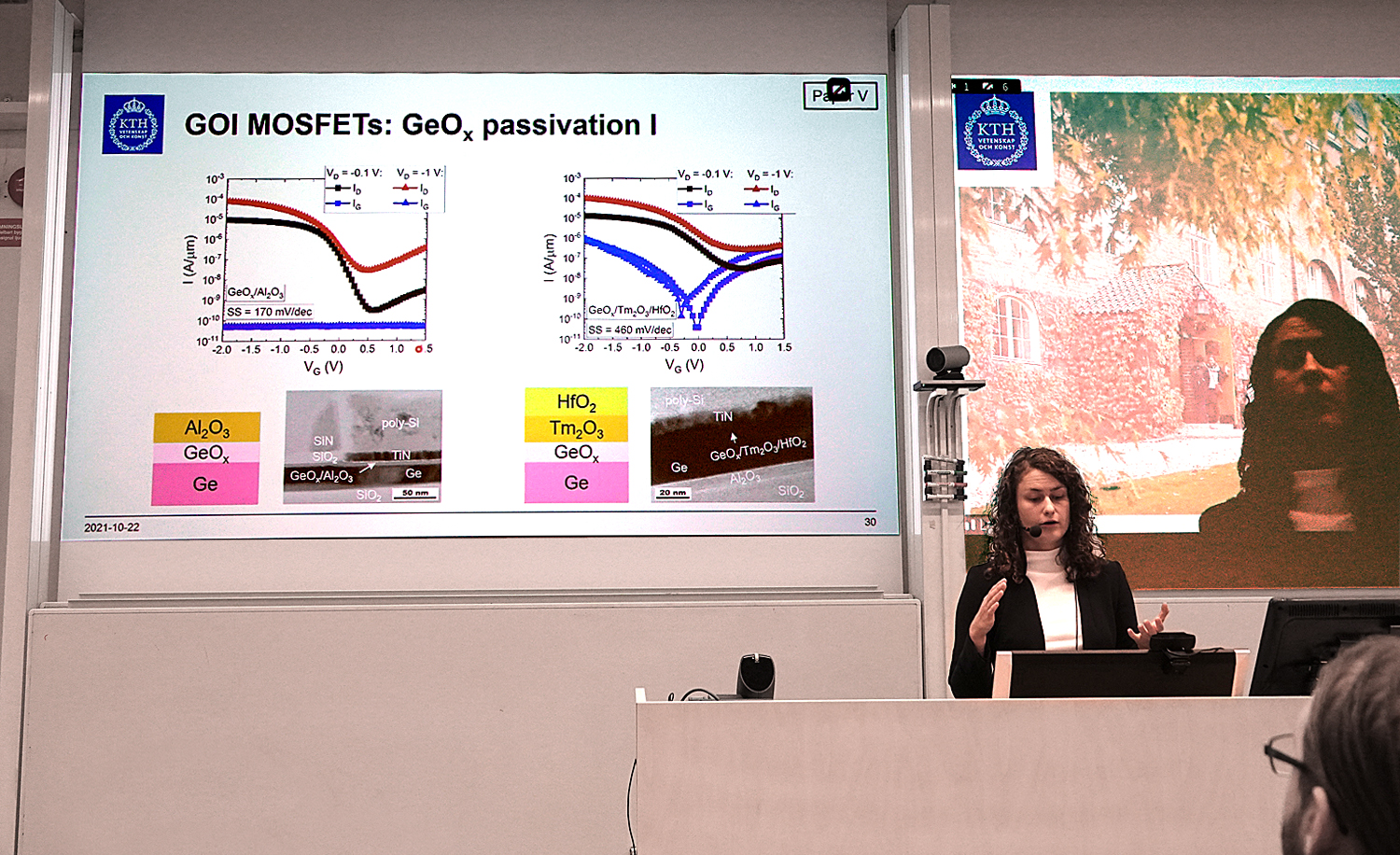

Här är det filosofie doktor Laura Žurauskaitė som visar upp sina resultat, tillsammans med handledaren Per-Erik Hellström. Mellan dem syns probstationen, mätutrustning som kan ansluta direkt till hennes kisel-germaniumchip och göra prestandamätningar.

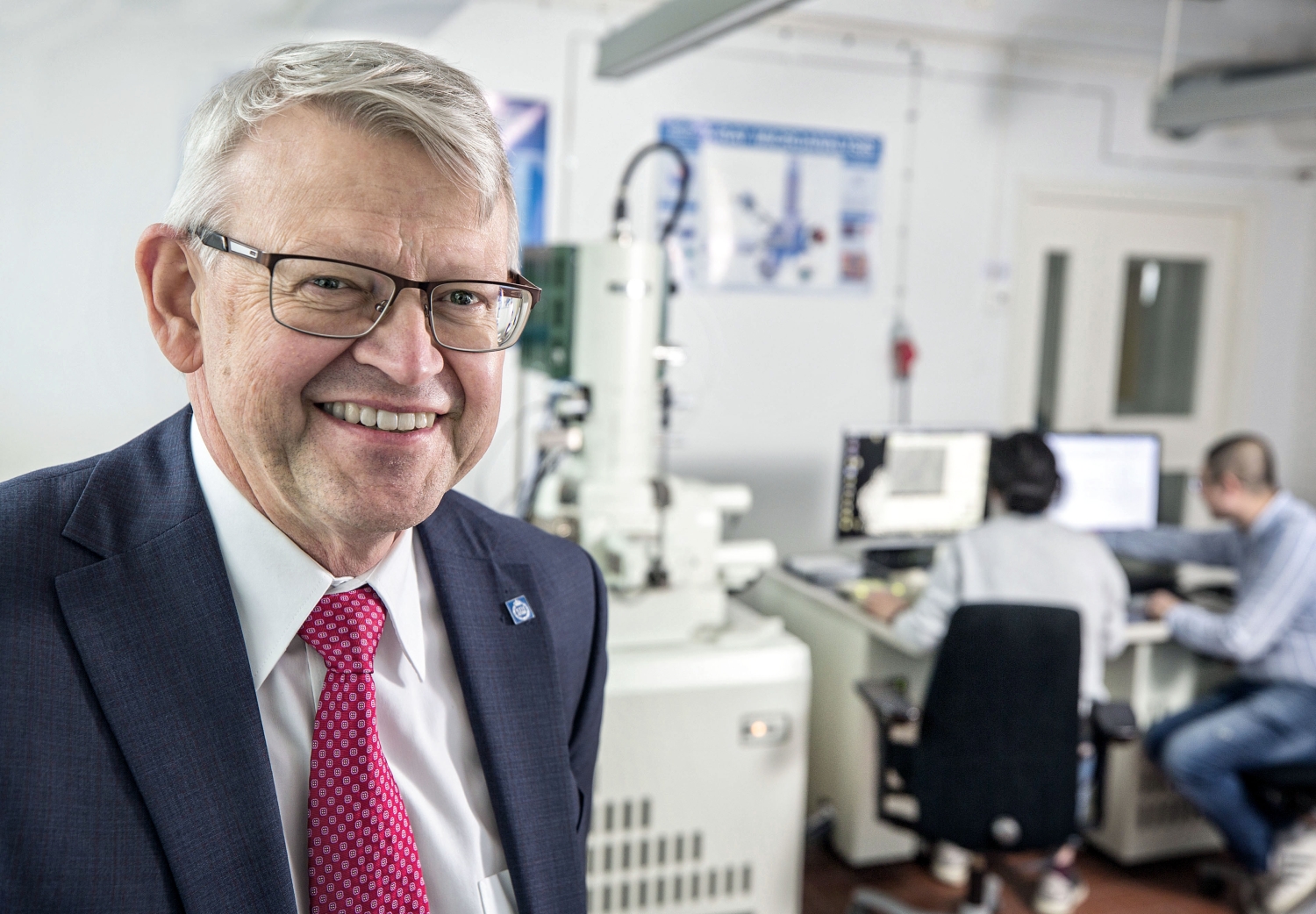

Efter fem års arbete har forskare på KTH Electrumlab under ledning av docent Per-Erik Hellström och professor Mikael Östling kunnat visa att man kan stapla flera lager av transistorer på varandra på en chip. Resultatet pekar på att det går att framställa kretsar med flera lager av transistorer och ledarmönster, och dessutom betydligt kortare ledningar mellan transistorerna än med vanliga platta tvådimensionella kretsar. Metoden kallas S3D (Sekvensiell 3D).

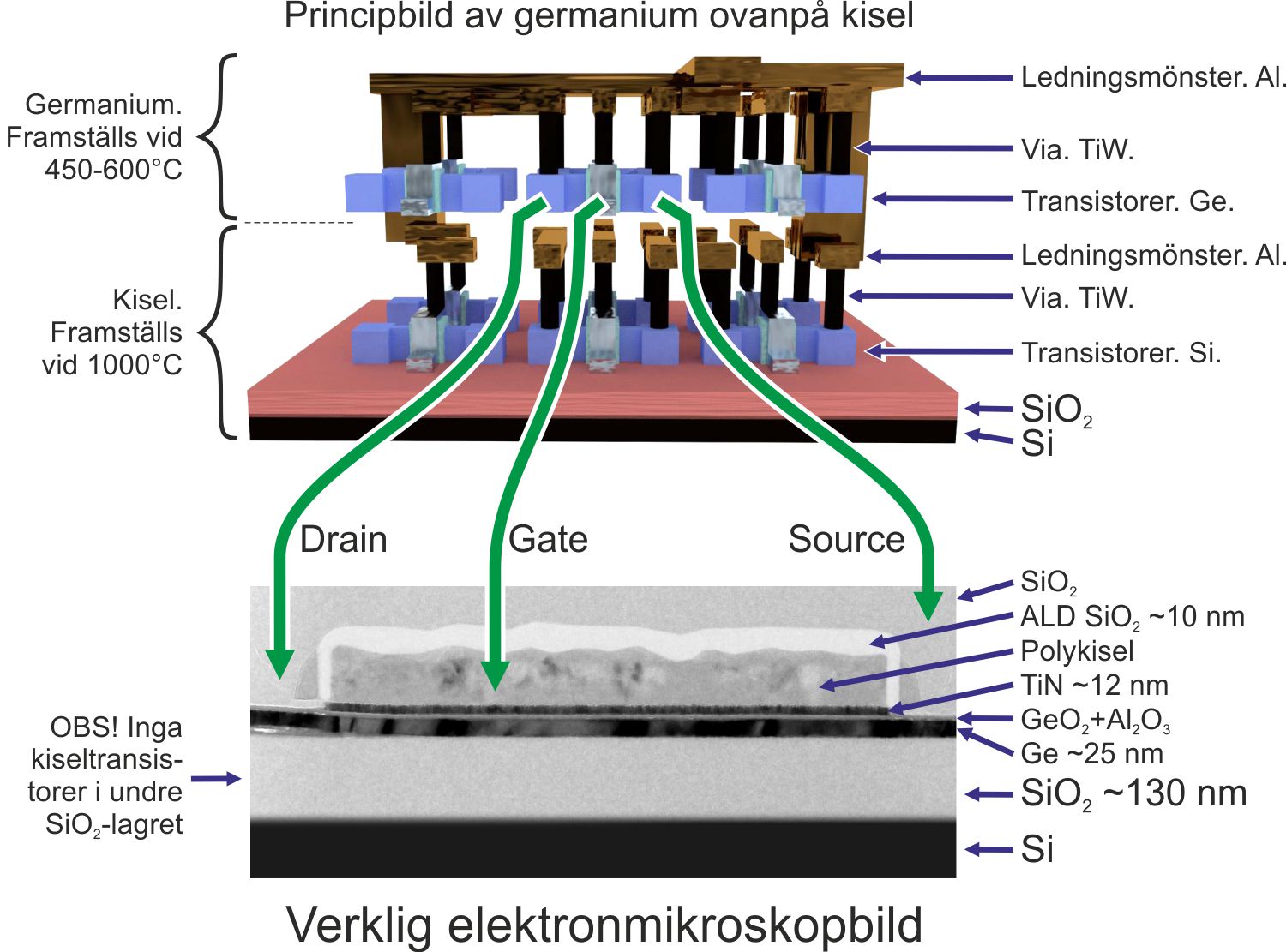

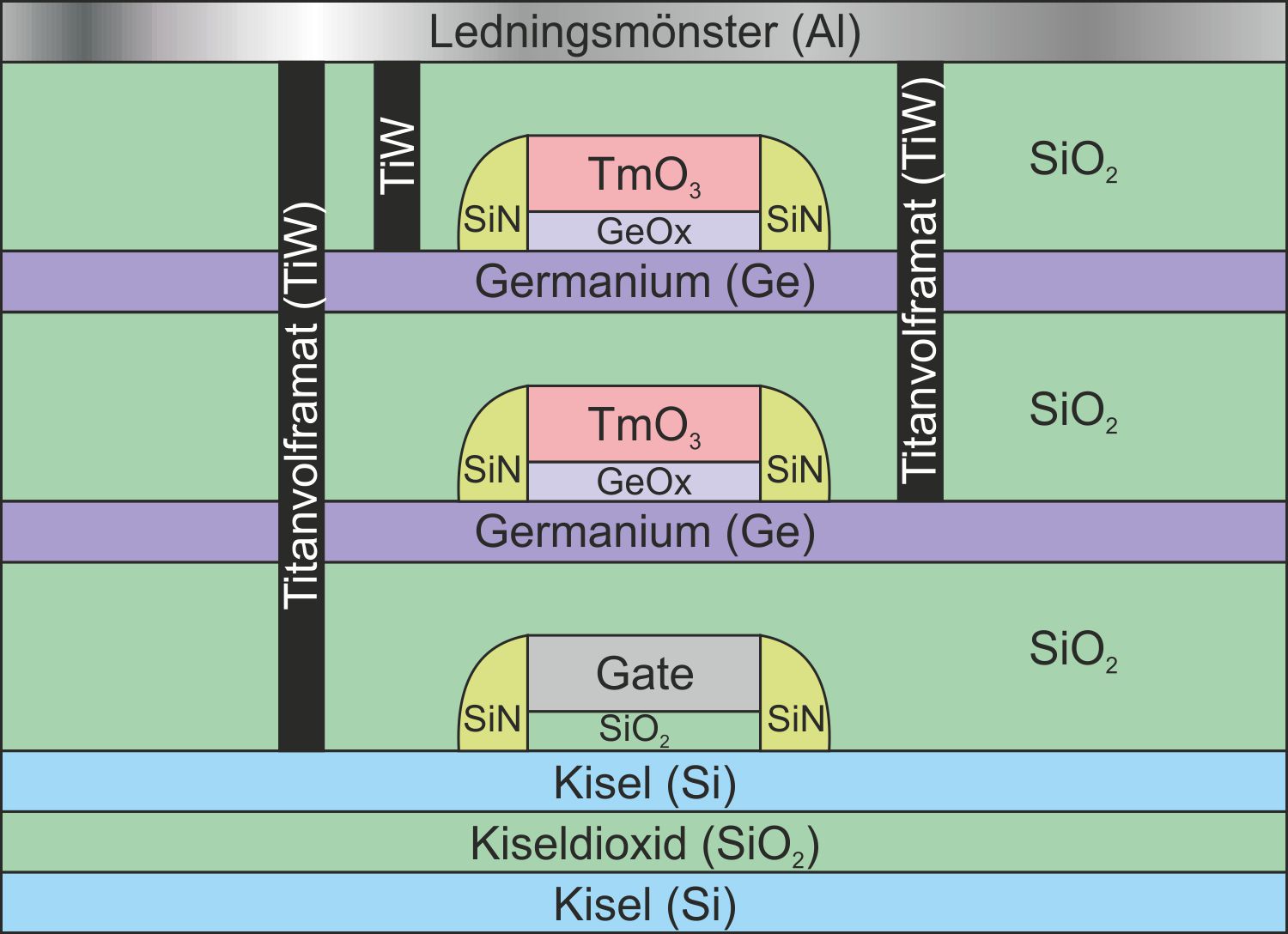

Grundmaterialet är kisel, men lagren man lägger på består av germanium. Det är av två anledningar. Germanium kan hanteras vid längre temperatur än kisel, sisådär 450-600 grader, så att man kan lägga på ett lager germanium ovanpå kisel utan att värma sönder mönstret i det underliggande kislet. Dessutom är germanium bättre än kisel för P-typ-transistorerna eftersom det uppvisar bättre hålmobilitet. Man gör alltså P-typ-transistorerna i germaniumskiktet och N-typ-transistorerna i kiselskiktet

IBM m fl löste en del av packningsproblemet genom att göra ledningsmönstret tredimensionellt och ha det ”i luften” ovanför transistorerna på kislet, så att man kunde tränga ihop transistorerna tätare. Men sedan tog det också slut. Vi talar nu om avstånd kring 5 nanometer.

Kan man till exempel stapla tio lager på varandra, vilket inte alls tycks orimligt, kan man uppnå samma täthet med 50 nanometers upplösning som man gör med gängse 5 nanometers-teknik, men till ett lägre pris, enklare utrustning och mindre ansträngning.

Grundforskning behövs

Kom ihåg att KTH ägnar sig åt grundforskning och att man inte är intresserade av någon färdig slutprodukt som det går att göra processorer med miljarder transistorer av.

Hade Intel eller Leti kunnat göra flerlagerskretsar på detta sätt, hade de redan gjort det. Men det kan de inte. Andra kan lägga kisel på kisel, men KTH har visat att det är möjligt att lägga germanium på kisel.

Avsikten är inte heller att producera jättekvantiteter, utan att ta reda på hur man gör och att det går. Staplingsprocessen är inte enkel. Det gäller att göra den industriellt användbar, vilket är viktigare än att börja tillverka processorer. Folket på Electrumlab har här banat väg för något helt nytt, som utan tvivel kommer att bli vägen framåt när den gängse tvådimensionella tekniken nått vägs ände. Moores lag gäller fortfarande.

Förluster och kapacitanser

All digital halvledarteknik går ut på att kunna switcha strömmar så snabbt som möjligt, för att kunna överföra så snabba pulståg som möjligt. Idag talar vi om omslagstider på pikosekunder.

Idealt ska en flank, en strömpuls kunna färdas från en transistor till nästa utan att störas eller absorberas av omgivningen eller av kretsen självt. När pulsen kommer fram en nanosekund senare ska den vara lika skarp och fin och med samma spänning som när den skapades. Tyvärr har alla ledningar induktans och kapacitans mot omgivningen och jordplanet, som kommer att ta åt sig en del av energin och göra flanken långsammare. Den absorberade energin blir till värme. Ledarna har resistans också, som direkt omvandlar den elektriska energin till värme. Ju längre ledaren är, desto mera energi kommer att absorberas och gå förlorad.

Långsamma flanker vill man inte ha för då måste man kompensera för problemet genom att mata in mera energi i kretsen och tvinga fram snabbare flanker. Matar man in mera energi blir kretsen varmare och till sist når man en gräns när kretsen inte tål att bli varmare. Den gränsen är nådd för länge sedan. Alternativet är att köra kretsen långsammare, vilket är kontraproduktivt.

Alltså måste man komma på ett sätt att göra kortare förbindelser mellan transistorerna. Dessutom måste förbindelserna ha låg resistans och ansluta till transistorerna på ett tillförlitligt sätt.

Lösningen: en smörgåstårta

Genom att stapla transistorerna på varandra i flera lager, snarare än att behöva bre ut dem bredvid varandra beräknar man att kunna minska förlusterna med ungefär 30 %. Sålunda har man lurat Moore och kunnat krympa kretsarna utan att egentligen krympa dem.

Överst i bilden ser du en tredimensionell visualisering av hur man tänker sig att stapla ett lager germaniumtransistorer ovanpå ett lager kiseltransistorer. Det undre lagret är en helt vanlig kiselkrets, som framställs med standardmetoder vid ungefär 1000 graders temperatur. Ovanpå denna har man staplat en germaniumkrets som framställs vid betydligt lägre temperaturer, 450-600 grader. Tvärs igenom halvledarlagren går förbindande vior. Ledningsmönstren som förbinder transistorer och vior kan vara av koppar eller aluminium.

Den undre bilden visar en verklig P-FET germaniumtransistor i genomskärning sedd i elektronmikroskop. Där ser du hur transistorn är konstruerad i detalj. Den tunna ljusgrå linjen består av germanium- och aluminiumoxid som utgör gate-oxiden, Notera dock att i denna bild finns inga kiseltransistorer i det undre lagret, då försöket bara gick ut på att testa staplingsproceduren.

Ett nyckelresultat har handlat om hur lagren och transistorerna förbinds med vior. Normalt använder man aluminium eller koppar, men med de låga processtemperaturer som används här, har det visat sig att både kobolt (Co) och titanvolfram (TiW) fungerar bra.

Hur man staplar lager på lager

Alltihop handlar om att lägga ett lager germanium ovanpå kiseldioxiden som ligger ovanpå kiselsubstratet (wafern, kiselbrickan) som innehåller kiseltransistorerna. Det är inte lätt, men det går. När man lagt på germaniet, kan man börja tillverka transistorer på det, med standardmetoder.

Det viktiga i processen är att kunna fästa germaniet ovanpå kislet utan att smälta de befintliga kiseltransistorerna, så att atomlagren driver iväg. Germaniumatomerna måste vilja fästa sig vid kiseldioxiden, atom invid atom, så att kristallstrukturerna inte störs. Dessutom måste man kunna fästa germaniet tillförlitligt över hela kiselsubstratet, så att man inte får områden med defekter.

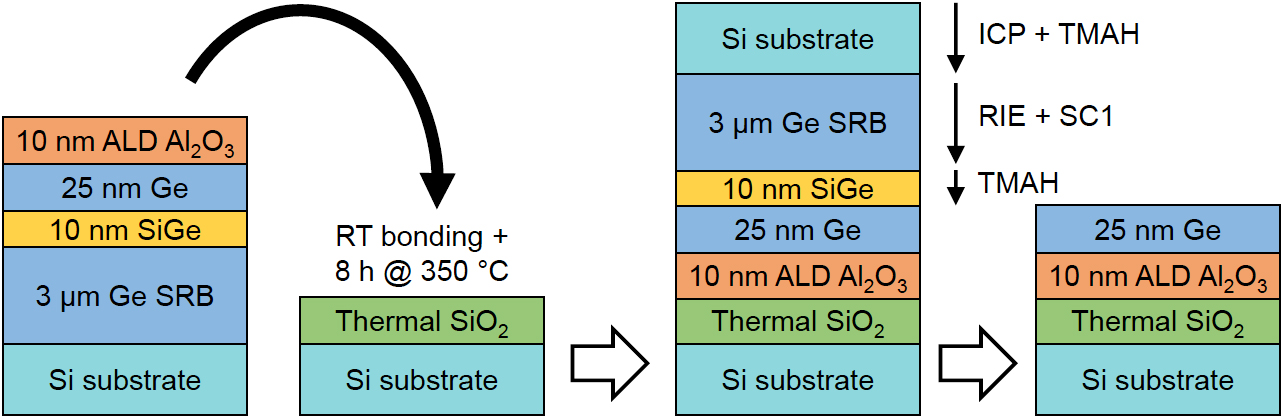

Man börjar med att täcka en tom kiselbricka, kallad donator, med 3 μm germanium för att ha en buffert (SRB) mot kislet. Germanium och kisel trivs nämligen inte ihop på atomnivå, utan gränssnittet blir kaotiskt. Ovanpå bufferten deponerar man ett antal lager, där lagret med 25 nm germanium är det som sedan ska användas. Ovanpå detta kommer ett lager med aluminiumoxid (Al2O3) som ska fungera som spärr för etsning i kommande steg.

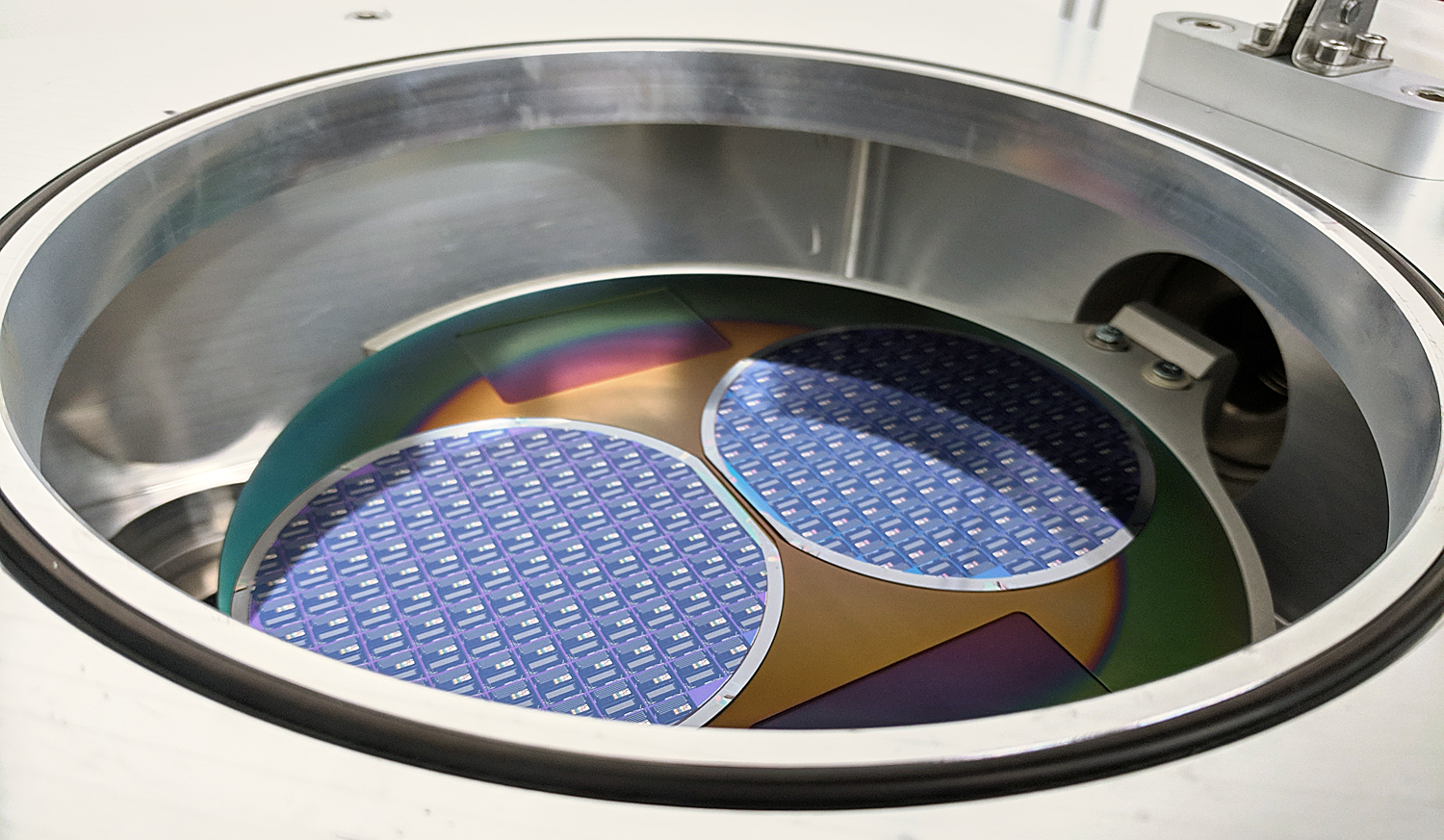

En metod att täcka kiselbrickan med olika metaller är ALD: Atomic Layer Deposition. Det görs i en depositionskammare som den på bilden ovan, där man blåser in olika gaser vid hög temperatur, till exempel gaser rika på kisel, germanium, hafnium, tulium eller andra metaller som ska deponeras. Metallerna i gaserna faller ut på kislet, atom invid atom, och man håller på så länge man anser sig behöva. På så sätt kan man lägga på önskat antal atomlager.

När donatorbrickan fått alla sina lager, vänds den och läggs ovanpå den andra, som alltså redan har ett kretsmönster. Nu rör vi oss på atomnivå. Så fort man lagt donatorbrickan ovanpå den andra, fäster de ihop på atomnivå och går inte att få isär igen, så det gäller att lägga dem rätt på en gång. Bidningen avslutas med bakning vid 350 graders temperatur. Med olika slip- och etsprocesser tar man därefter bort de översta tre lagren.

Kvar finns bara ett 25 nanometer tjockt lager i germanium på vilket man kan börja skapa sina transistorer, genom att lägga på fotoresist, exponera och etsa fram transistorstrukturer och dopa dem med gängse metoder för halvledarframställning.

Det hela är knepigare än så, men detta är huvuddragen.

Flera lager

Denna studie hade för avsikt att visa att det gick att lägga ett lager germaniumtransistorer ovanpå ett lager kisel, men det finns inget principiellt skäl mot att inte kunna lägga hur många lager som helst på varandra.

Då skulle ett tvärsnitt kunna se ut så här, med exempelvis tre FET-transistorer på varandra. Givetvis kan man lägga ledningsmönster mellan de olika halvledarlagren också, men du ser ändå principen med korta vior.

Med möjligheten att stapla på höjden kan man också få ökad funktionalitet med logik i botten följt av minne och kanske sensorer och lasrar på toppen.

Värmeproblem

Hur gör man med värmen? En tvådimensionell krets med en miljon transistorer blir väl lika varm som en tredimensionell krets med lika många transistorer med samma funktion? Och sen då, när den tredimensionella tekniken medger mångfalt fler transistorer, hur blir man av med värmen?

Nu visar det sig att de kortare viorna i S3D faktiskt kan minska värmeförlusterna i och med att de är kortare och därmed ger lägre resistans och minskade förluster i övrigt. Man räknar med en minskning på 30 %. S3D-Kretsar lovar alltså att bli effektsnålare än tvådimensionella.

Men snart kommer tillverkarna att stapla ännu fler transistorer på varandra och värmeförlusterna kommer att bli ännu större. Hur man ska lösa det, har forskarna inte funderat på, men någon form av vätskekylning torde bli aktuell om man ska föra bort flera hundra watt.

CAD-modeller i 3D

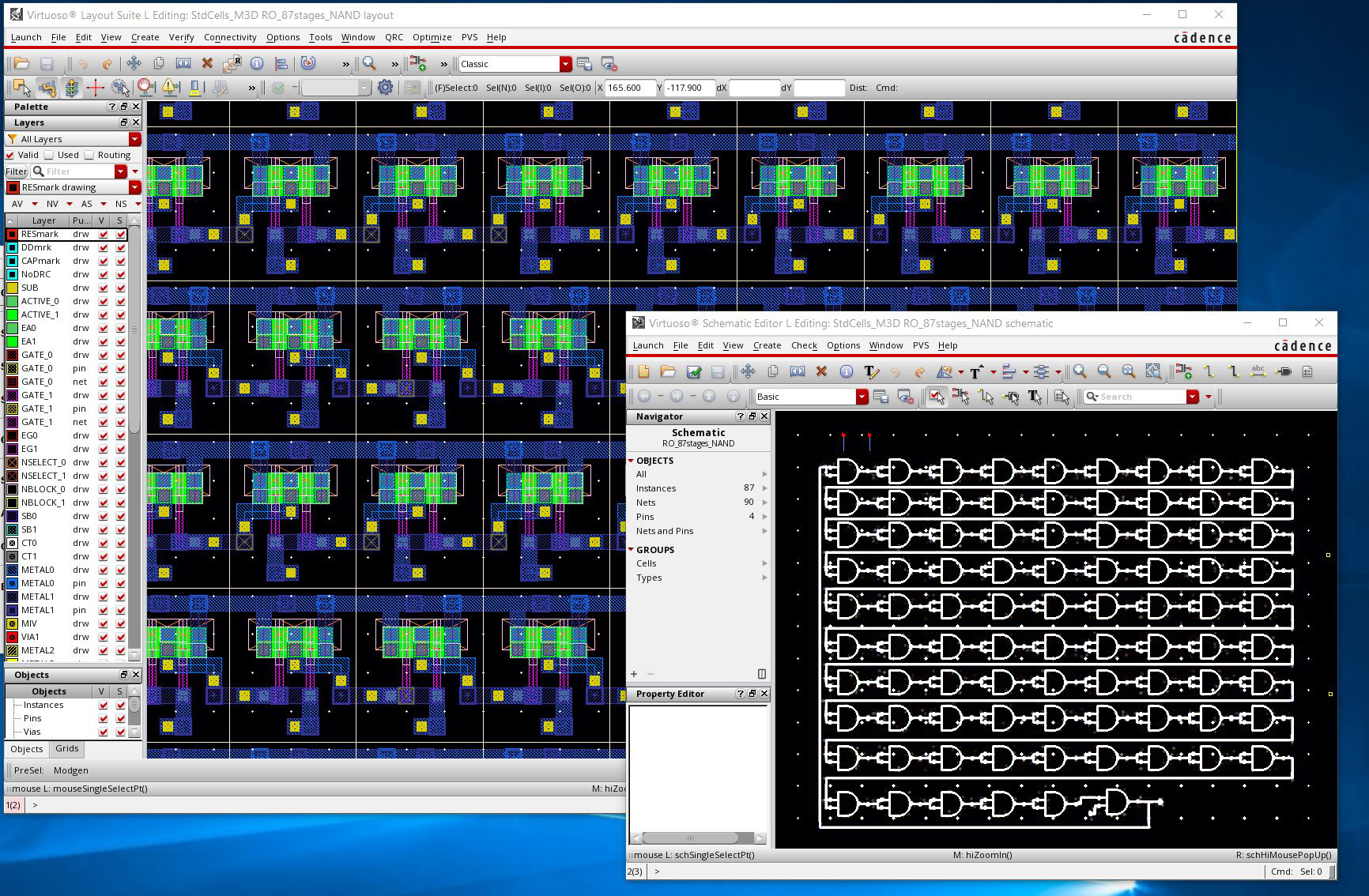

Naturligtvis är det ingen som ritar och optimerar 3D-kretsarna för hand, utan KTH-forskaren Panagiotis Chaourani har utvecklat ett CAD-system som används för att konstruera och koppla samman kretsarna, varefter mönstret överförs direkt till tillverkningsmaskinerna.

Skärmbilden visar CAD-systemet Virtuoso, där man gjort en layout av en sk ringoscillator, den enklaste elektroniska krets som kan tänkas, som består av en rad seriekopplade NAND-grindar som används för att testa hur snabba transistorerna är. Den lilla rutan visar själva kopplingen, medan bakgrundsbilden är den färdiga layouten som ska överföras till germanium.

Ju närmare transistorerna kommer varandra, desto större risk är det att en strömpuls i en transistor kopplar sig till transistorn inunder via kapacitiv koppling och skulle kunna införa brus i kretsarna eller få den andra transistorn att öppna slumpmässigt.

När detta arbete påbörjades fanns inget CAD-program som kunde ta hänsyn till den speciella störsituation som uppstår då man packar ett antal lager transistorer på varandra på 100 nanometers avstånd, så under utvecklingsarbetet har man fått placera transistorerna för hand.

Störproblemet finns även i tvådimensionella kretsar och har redan åtgärdats i de gängse CAD-programmen, men nu kommer den tredje dimensionen och för det finns ännu ingen automatiserad lösning. CAD-programmen måste modifieras till att ta hänsyn till alla lagren och placera transistorerna så att de inte ligger mitt ovanpå varandra, utan lämpligt sick-sackade.

Studenterna på KTH ger sig inte så lätt, utan en vidareutveckling av CAD-systemet är på gång, som ska kunna hantera problemet automatiskt. Ytterligare forskning behövs för att hitta andra metoder att minska den kapacitiva kopplingen.

En färdig krets

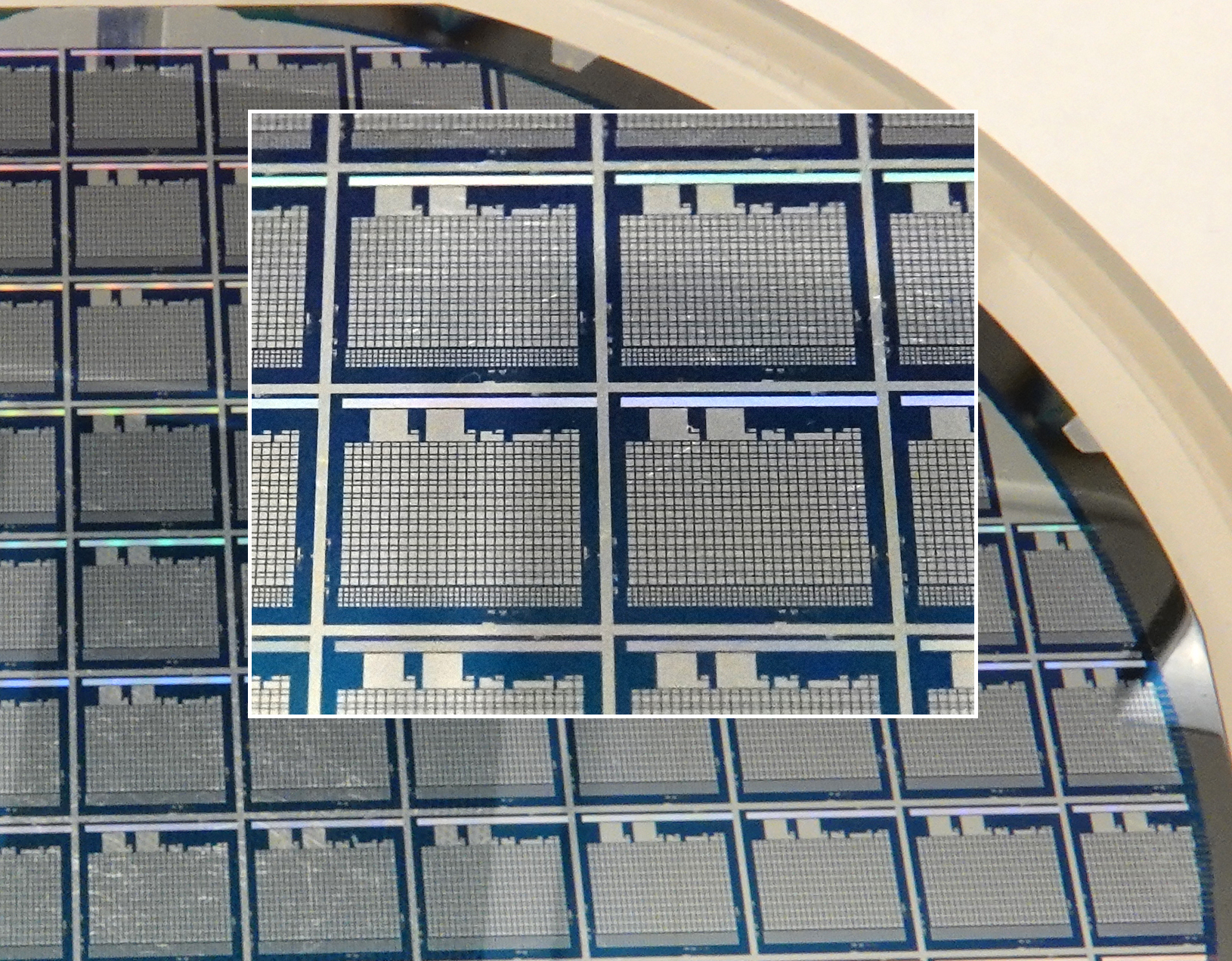

Hittills har Myfab-labbet producerat ett antal testkretsar med huvudsyfte att kunna mäta upp transistorernas prestanda och hur den skiljer sig för olika framställningsmetoder.

Bilden visar en testkrets med ett regelbundet mönster av transistorer. De små fyrkantiga metalliserade plättarna är anslutningar till enskilda transistorer (som är för små för att synas). De ligger regelbundet utlagda sida vid sida i massupplaga för att kunna testas av en testrobot, även den utvecklad av en KTH-student.

Kiselbrickan läggs in i en probstation och förses med matningsspänning, varefter man sänker ned elektroder mot de enskilda kontaktpunkterna och testar transistor för transistor.

Resultat

Dr. Laura Žurauskaitė har visat att det kan gå att stapla ett antal lager germaniumtransistorer på varandra. Men mera utveckling kommer att krävas för att få gränssnittet mellan germanium och kisel tillförlitligt och stabilt.

Går det att få bibehållna prestanda (läckströmmar, frekvenssvar etc) med transistorer i flera lager? Frågan är med ”kanske” för närvarande besvarad.

Går det att säkra gränssnittet mellan germanium och kisel finns det chanser att germaniumtransistorerna får bättre prestanda än gängse kiseltransistorer.

Forskningsarbetet är inte på något sätt avslutat. Om doktoranderna på KTH slutligen löser problemet med gränssnittet mellan kisel och germanium kan resultatet bli:

- Ännu fler transistorer, alltså flera logiska funktioner på en chip

- Mindre kretsar

- Kallare kretsar

- Lägre energiförbrukning

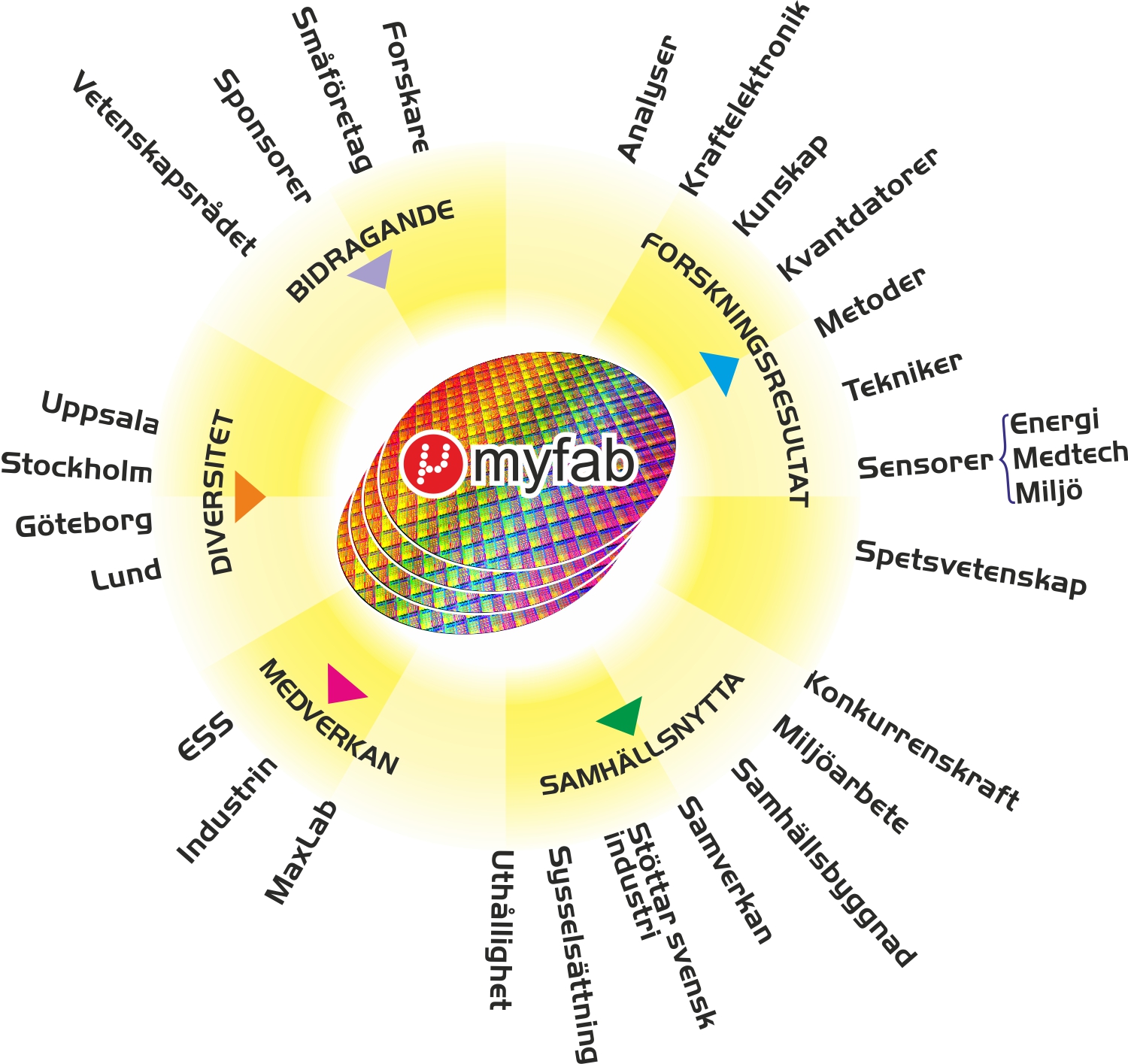

Fördelar för svensk industri

Svensk halvledarforskning har gott rykte på världsmarknaden. Arbetet vid det svenska Myfab-konsortiet har resulterat i många doktorsavhandlingar och artiklar i facktidskrifter om nya metoder för halvledartillverkning. Detta leder i sin tur till att industrin gärna sponsrar forskningen vid Myfab, vilket i sin tur leder till ännu flera doktorander med världsrykte, osv. En uppåtgående spiral.

Det viktigaste med allt arbete med S3D är att man utvecklat en doktorandkurs i avancerad CMOS-teknik som gjort KTH till en betydande partner i det europeiska forskningssamarbetet kring S3D. För närvarande har projektet genererat fyra doktorsavhandlingar och fyra civilingenjörer, och flera är på väg.

Här disputerar Laura Žurauskaitė i ämnet ”Ge/high-k Gates for Monolithic 3D Integration”. Flera opponenter från olika europeiska universitet ansatte henne med frågor om arbetet, men till sist enades de samlade professorerna om att hon uppfyllde kraven och hon fick sin doktorsgrad.

Efter utbildningen kommer KTH-doktoranderna att sprida sig till olika teknikföretag i Sverige och därigenom bidra till den svenska industrin och landets nystartade företag. Några av dem ger sig också ut i världen och kunskaperna vandrar från Myfab-laboratorierna till den sameuropeiska forskningsorganisationen EuroNanoLab och amerikanska Intel, franska Leti och så vidare. Det är på det sättet svenska universitet skapar en vinst för Sverige.

Förhoppningsvis kan detta få svenska företag att satsa på tillhörande avancerad teknologi, som kan locka hem studenterna till Sverige igen.

Läs mer

För mera information, ta kontakt med docent Per-Erik Hellström, pereh@kth.se eller professor Mikael Östling, mostling@kth.se.

Förstå Myfabs betydelse för svensk industri: https://www.teknikaliteter.se/2020/11/05/sveriges-framtid-i-dina-hander/

Myfab är redo för landning på Venus: https://www.teknikaliteter.se/2020/04/14/working-on-venus-levererar/

En mycket djupare genomgång finns i forskaren Panagiotis Chaouranis doktorsavhandling ”Sequential 3D Integration – Design Methodologies and Circuit Techniques” som kan hittas på http://www.diva-portal.org/smash/get/diva2:1317812/FULLTEXT01.pdf

Projektet har finansierats med anslag från SSF (Stiftelsen för Strategisk Forskning) till professor Mikael Östling.